48kHz input. The stereo DAC can also be used while the voice codec is in use. The headphone amplifier delivers  $25mW_{BMS}$  to a  $32\Omega$  single-ended stereo load with less than Total shutdown of

**Boomer**<sup>®</sup> Audio Power Amplifier Series

Audio Subsystem with Stereo Headphone & Mono

# **Features**

- 16-bit resolution 48kHz stereo DAC

- 16-bit resolution 8kHz voice codec

- I<sup>2</sup>S digital audio data serial interface

- Two-wire serial control interface

- PCM voice audio data serial interface

- 25mW/channel stereo headphone amplifier

- 330mW mono 8Ω amplifier (at AV<sub>DD</sub> = 3.0V)

- 32-step volume control for audio output amplifiersNo snubber networks or bootstrap capacitors are

- required by the headphone or hands-free amplifiersDigital sidetone generation with adjustable attenuation

- Gain controllable headphone amp, mono BTL amp, mic preamp

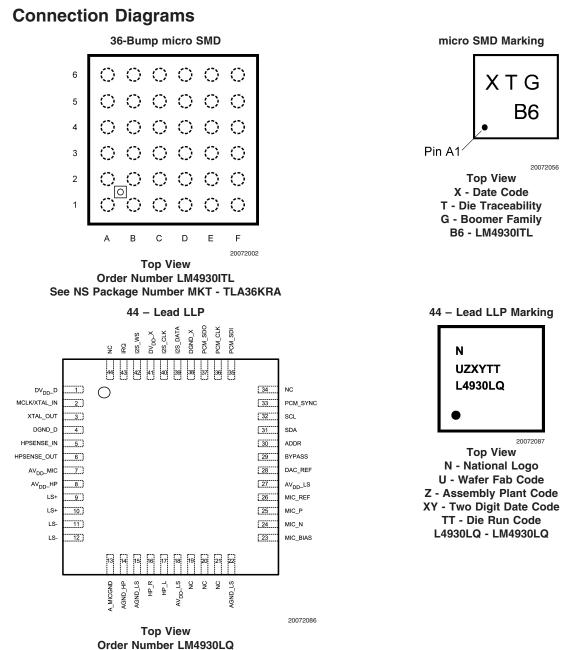

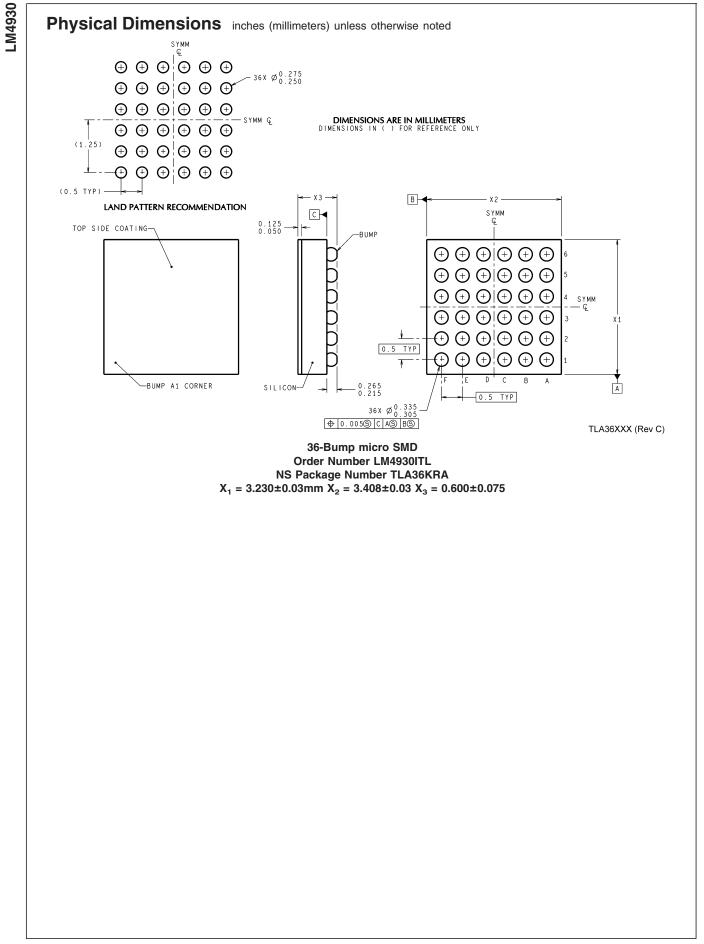

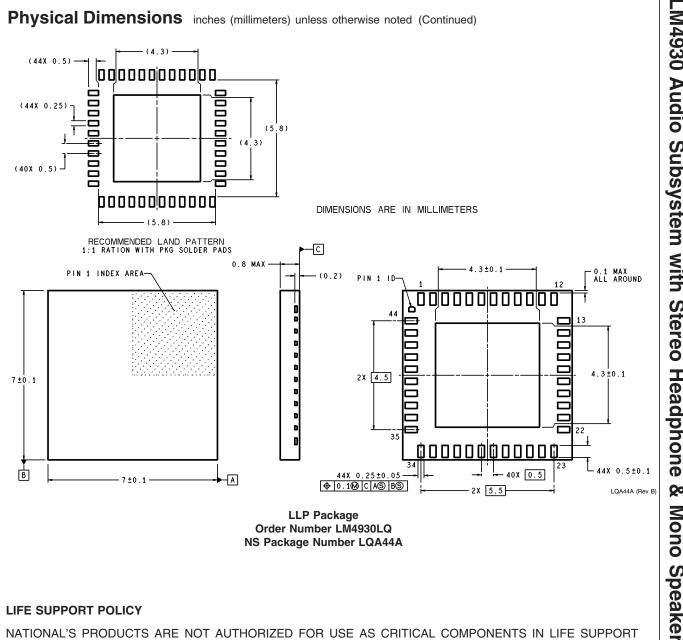

- Available in the 36-bump micro SMD and 44-lead LLP packages

# **Applications**

- Mobile Phones

- Mobile/low power audio appliances

- PDAs

auirement.

N**ational** Semiconductor

**Speaker Amplifiers**

in mobile phones and other portable devices.

less than 1% distortion when  $AV_{DD} = 3V$ .

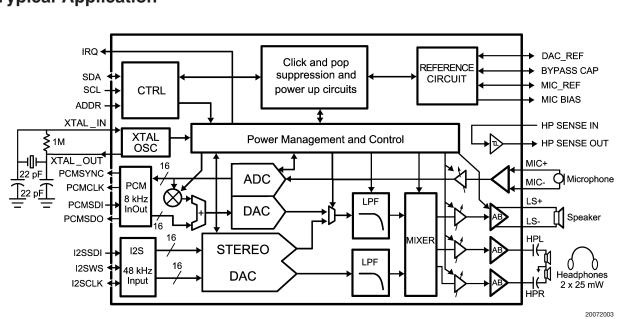

The LM4930 is an integrated audio subsystem that supports voice and digital audio functions. The LM4930 includes a high quality I<sup>2</sup>S input stereo DAC, a voice band codec, a stereo headphone amplifier and a high-power mono speaker

amplifier. It is primarily designed for demanding applications

The LM4930 features an I<sup>2</sup>S serial interface for full range audio, a 16-bit PCM bi-directional serial interface for the voice band codec and an two-wire interface for control. The full range music path features an SNR of 86dB with a 16-bit

0.5% distortion (THD+N) when  $AV_{DD} = 3V$ . The mono

speaker amplifier delivers up to 330mW into an  $8\Omega$  load with

The LM4930 employs advanced techniques to reduce power

consumption, to reduce controller overhead and to eliminate click and pop. Boomer audio power amplifiers were de-

signed specifically to provide high quality output power with

a minimal amount of external components. It is, therefore,

ideally suited for mobile phone and other low voltage appli-

cations where minimal power consumption is a primary re-

**General Description**

LM4930

# Key Specifications

| $P_{LS\ OUT}$ at $AV_{DD}$ = 5.0V, 8 $\Omega$ |          |

|-----------------------------------------------|----------|

| 1% THD+N                                      | 1W (typ) |

| • $P_{LS OUT}$ at $AV_{DD}$ = 3.0V, 8 $\Omega$                              |             |

|-----------------------------------------------------------------------------|-------------|

| 1% THD+N                                                                    | 330mW (typ) |

| $\blacksquare$ P <sub>H/P OUT</sub> at AV <sub>DD</sub> = 3.0V, 32 $\Omega$ |             |

| $F_{H/P OUT}$ at $Av_{DD} = 5.0v$ , $5232$ |                                                                 |

|--------------------------------------------|-----------------------------------------------------------------|

| 0.5% THD+N                                 | 25mW (typ)                                                      |

| Supply voltage range                       |                                                                 |

| DV <sub>DD</sub> (Note 8)                  | 2.6V to 4.5V                                                    |

| AV <sub>DD</sub> (Note 8)                  | 2.6V to 5.5V                                                    |

|                                            | 0.5% THD+N<br>Supply voltage range<br>DV <sub>DD</sub> (Note 8) |

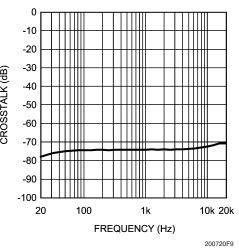

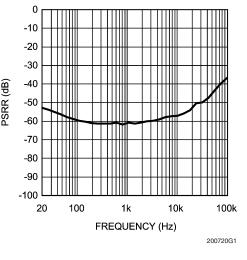

Total shutdown current $2\mu A$  (typ)PSRR at 217Hz,  $AV_{DD} = 3V$ 50dB (typ)

September 2004

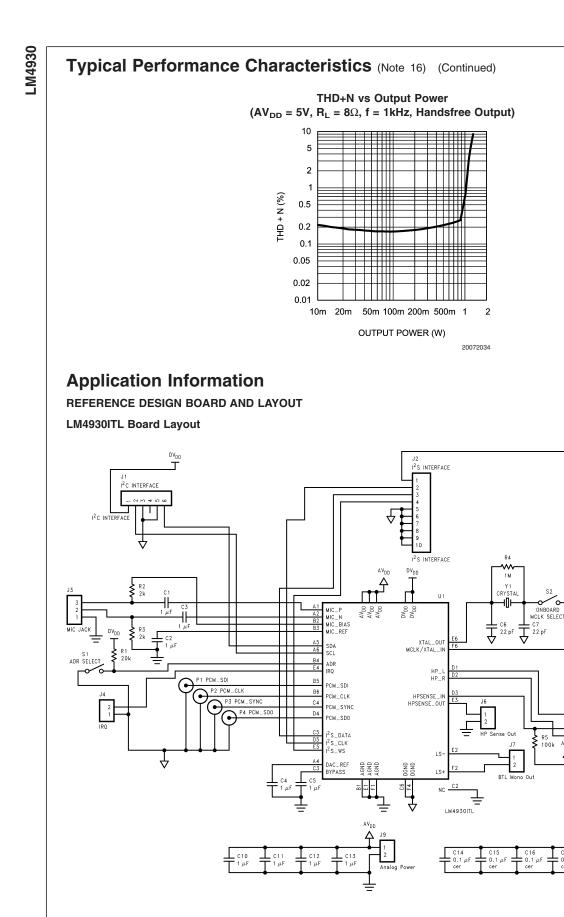

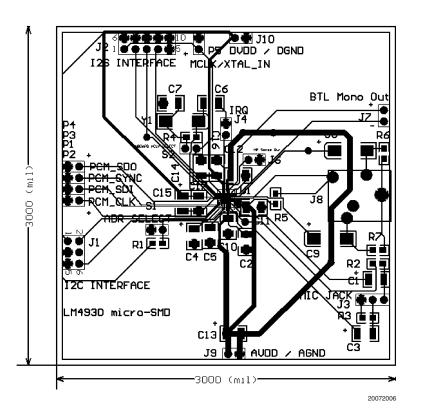

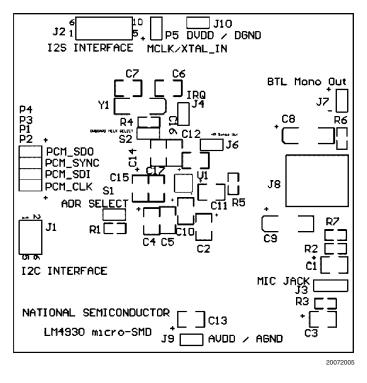

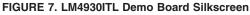

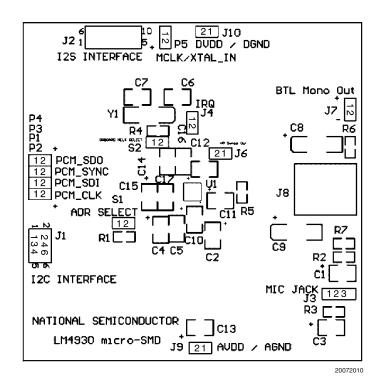

FIGURE 1. Typical I<sup>2</sup>S + Voice codec application circuit for mobile phones

**B6**

20072087

20072056

See NS Package Number MKT - LQA44A

| 0 |

|---|

| က |

| ດ |

| 4 |

| ⋝ |

| _ |

|   |

# Pin Descriptions

| Pin | Descriptions |                                                                                                                                                                    |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | MIC_P        | Microphone positive differential input                                                                                                                             |

| A2  | MIC_N        | Microphone negative differential input                                                                                                                             |

| A3  | AVDD_MIC     | Analog V <sub>dd</sub> for microphone preamp                                                                                                                       |

| A4  | DAC_REF      | D/A converter reference voltage                                                                                                                                    |

| A5  | SDA          | Two-wire control interface serial data pin                                                                                                                         |

| A6  | SCL          | Two-wire control interface serial clock pin                                                                                                                        |

| B1  | AGND_MIC     | Analog ground for microphone preamp                                                                                                                                |

| B2  | MIC_BIAS     | Microphone bias supply output (2V)                                                                                                                                 |

| B3  | MIC_REF      | Internal fixed-reference bypass capacitor decoupling pin                                                                                                           |

| B4  | ADDR         | Control bus address select pin                                                                                                                                     |

| B5  | PCM_SDI      | PCM serial data in                                                                                                                                                 |

| B6  | PCM_CLK      | PCM Serial clock pin                                                                                                                                               |

| C1  | AVDD_HP      | Analog V <sub>dd</sub> for headphone amplifier                                                                                                                     |

| C2  | NC           | No Connect                                                                                                                                                         |

| C3  | BYPASS       | Half-supply bypass capacitor decoupling pin                                                                                                                        |

| C4  | PCM_SYNC     | PCM Frame sync pin                                                                                                                                                 |

| C5  | I2S_DATA     | I <sup>2</sup> S serial data input                                                                                                                                 |

| C6  | DGND_D       | Digital ground                                                                                                                                                     |

| D1  | HP_L         | Headphone amplifier connection (Left)                                                                                                                              |

| D2  | HP_R         | Headphone amplifier connection (Right)                                                                                                                             |

| D3  | HPSENSE_IN   | Connection for sense pin of headphone jack                                                                                                                         |

| D4  | PCM_SDO      | PCM serial data out                                                                                                                                                |

| D5  | I2S_CLK      | I <sup>2</sup> S serial bit clock                                                                                                                                  |

| D6  | DVDD_D       | Digital V <sub>dd</sub>                                                                                                                                            |

| E1  | AGND_HP      | Analog ground for headphone amplifier                                                                                                                              |

| E2  | LS-          | Loudspeaker amplifier BTL negative out (-)                                                                                                                         |

| E3  | HPSENSE_OUT  | Logic output pin to indicate headphone connection status. Outputs logic high when<br>HPSENSE_IN is high and outputs logic low when HPSENSE_IN is low. See Figure 5 |

|     | 150          | for suggested application circuit                                                                                                                                  |

| E4  | IRQ          | LM4930 mode status indicator pin                                                                                                                                   |

| E5  | I2S_WS       | I <sup>2</sup> S word select                                                                                                                                       |

| E6  | XTAL_OUT     | Negative feedback source for external crystal MCLK                                                                                                                 |

| F1  | AGND_LS      | Analog ground for loudspeaker amplifier                                                                                                                            |

| F2  | LS+          | Loudspeaker amplifier BTL positive out (+)                                                                                                                         |

| F3  | AVDD_LS      | Analog V <sub>DD</sub> for loudspeaker amplifier                                                                                                                   |

| F4  | DGND_X       | Digital ground                                                                                                                                                     |

| F5  | DVDD_X       | Digital V <sub>DD</sub>                                                                                                                                            |

| F6  | MCLK/XTAL_IN | 12.288MHz or 24.576MHz Master Clock from crystal (via XTAL OUT) or external source                                                                                 |

# **System Control Registers**

The LM4930 is controlled with a two-wire serial interface. This interface is used to configure the operating mode, digital interfaces, and delta-sigma modulators. The LM4930 is controlled by writing information into a series of write-only registers, each with its own unique 7 bit address. The following registers are programmable:

# **BASIC CONFIG REGISTER**

This register is used to configure the I<sup>2</sup>S and PCM interfaces as well as the 48kHz DAC module. The 7 bit address for the BASICCONFIG register is XX10000. (X = 0 if ADDR is set to logic 0) (X = 1 if ADDR is set to logic 1)

# BASIC CONFIGURATION (XX1000). (Set = logic 1, Clear = logic 0)

| 571010 0 | 011110010 |    |    | (001 - | iogio i | , 0104 | - 109 |   |   |   |   |   |   |   |   |   |

|----------|-----------|----|----|--------|---------|--------|-------|---|---|---|---|---|---|---|---|---|

| BIT      | 15        | 14 | 13 | 12     | 11      | 10     | 9     | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RESET    | 0         | 0  | 0  | 0      | 0       | 0      | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |           |    |    |        |         |        |       |   |   |   |   |   |   |   |   |   |

| Address | Register      | Descriptio          | n                                                   |                       |                           |                                                            |

|---------|---------------|---------------------|-----------------------------------------------------|-----------------------|---------------------------|------------------------------------------------------------|

| 3:0     | MODE          | The LM49            | 30 can be placed in on                              | e of several modes    | that dictate the basic    | operation. When                                            |

|         |               | new mode            | is selected the LM493                               | 0 will change operat  | tion silently and will re | -configure the                                             |

|         |               | power mar           | nagement profile autom                              | natically. The modes  | are described as follo    | ws: (Note 14)                                              |

|         |               | Mode                | Mono Speaker                                        | Headphone Left        | Headphone Right           | Comment                                                    |

|         |               |                     | Amplifier Source                                    | Source                | Source                    |                                                            |

|         |               | 0000                | None                                                | None                  | None                      | Powerdown mod                                              |

|         |               | 0001                | None                                                | None                  | None                      | Standby mode                                               |

|         |               | 0010                | Voice                                               | None                  | None                      | Mono speaker<br>mode                                       |

|         |               | 0011                | None                                                | Voice                 | Voice                     | Headphone call mode                                        |

|         |               | 0100                | Voice                                               | Voice                 | Voice                     | Conference call mode                                       |

|         |               | 0101                | Audio (L+R)                                         | None                  | None                      | L+R mixed to<br>mono speaker                               |

|         |               | 0110                | None                                                | Audio (Left)          | Audio (Right)             | Headphone<br>stereo audio                                  |

|         |               | 0111                | Audio (L+R)                                         | Audio (Left)          | Audio (Right)             | L+R mixed to<br>mono speaker +<br>stereo headphor<br>audio |

|         |               | 1000                | Audio (Left)                                        | Voice                 | Voice                     | Mixed Mode                                                 |

|         |               | 1001                | Voice + Audio<br>(Left)                             | Voice                 | Voice                     | Mixed mode                                                 |

|         |               | 1010                | Voice                                               | Audio (Left)          | Audio (Left)              | Mixed Mode                                                 |

| 4       | SOFT_RESET    | Resets the          | LM4930, excluding th                                | e control registers   |                           |                                                            |

| 5       | PCM_LONG      | If set the F        | PCM interface uses a lo                             | ong frame sync. (No   | te 12)                    |                                                            |

| 6       | PCM_COMPANDED | If set the 8<br>12) | MSBs are presumed                                   | to be companded da    | ita and the 8 LSBs are    | e ignored. (Note                                           |

| 7       | PCM_LAW       | If set, the         | companded G711 data                                 | is set to be A-law, e | else µ-law is assumed     | (Note 12)                                                  |

| 8:9     | PCM_SYNC_MODE |                     | h), 2 (01h) or 4(10h) 1<br>rames. (Note 12)         | 6 bit frames per syn  | c. The PCM_SDO pin        | is tri-stated durin                                        |

| 10      | PCM_ALWAYS_ON |                     | ould be set if another o<br>lock and sync signals i |                       |                           |                                                            |

| 11      | I2S_M/S       | I2S master          | r or slave select. If set                           | then I2S = master. (  | Cleared = slave           |                                                            |

| 12      | I2S_RES       | I2S resolut         | ion select. If set then 3                           | 32 bits per frame. If | cleared then 16 bits p    | er frame                                                   |

| 13      | RSVD          | RESERVE             | D (Note 13)                                         |                       |                           |                                                            |

| 14      | RSVD          | RESERVE             | D (Note 13)                                         |                       |                           |                                                            |

| 15      | RSVD          | RESERVE             | D (Note 13)                                         |                       |                           |                                                            |

# System Control Registers (Continued)

# **VOICE/TEST CONFIG REGISTERS**

This register configures the voiceband codec, sidetone attenuation, and selected control functions. The 7 bit address for the VOICE TESTCONFIG register is XX10001. (X = 0 if ADDR is set to logic 0) (X = 1 if ADDR is set to logic 1)

# VOICETESTCONFIG (XX10001). (Set = logic 1, Clear = logic 0)

|               |   | . , | •  |    |    |    | · · |   |   |   |   |   |   |   |   |   |

|---------------|---|-----|----|----|----|----|-----|---|---|---|---|---|---|---|---|---|

| <b>BIT</b> 15 |   | 14  | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RESET 0       | ( | 0   | 0  | 0  | 0  | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Address | Register        | Description   | n                       |                     |                                              |             |

|---------|-----------------|---------------|-------------------------|---------------------|----------------------------------------------|-------------|

| 0       | CLASS           | If set, confi | gures the chip for u    | se with an exter    | nal class D or linear amplifier and turns th | ne          |

|         |                 | BTL speake    | er output into a buff   | er. (Note 12)       |                                              |             |

| 4:1     | SIDESTONE_ATTEN | Programs t    | he attenuation of th    | e digital sidetone  | e. Attenuation is set as follows:            |             |

|         |                 | 4:1           | Sidetone                | 4:1                 | Sidetone Attenuation                         |             |

|         |                 |               | Attenuation             |                     |                                              |             |

|         |                 | 0000          | Mute                    | 1000                | -9dB                                         |             |

|         |                 | 0001          | -30dB                   | 1001                | -6dB                                         |             |

|         |                 | 0010          | -27dB                   | 1010                | -3dB                                         |             |

|         |                 | 0011          | -24dB                   | 1011                | 0dB                                          |             |

|         |                 | 0100          | -21dB                   | 1100                | Mute                                         |             |

|         |                 | 0101          | -18dB                   | 1101                | Mute                                         |             |

|         |                 | 0110          | -15dB                   | 1110                | Mute                                         |             |

|         |                 | 0111          | -12dB                   | 1111                | Mute                                         |             |

| 5       | AUTOSIDE        | This feature  | e is included for use   | with the mono       | speaker in hands-free applications where     |             |

|         |                 | sidetones n   | nay not be desirable    | e. If set, the side | tone is always muted in modes when voi       | ce i        |

|         |                 | 1             |                         |                     | 1, and 1010), otherwise the sidetone is p    | rese        |

|         |                 |               | r level is set in the a |                     | -                                            |             |

| 6       | CLOCK_DIV       |               | s for the use of a 2    | 4.576MHz crysta     | al. Default setting is for 12.288MHz crysta  | <b>ι</b> Ι. |

|         |                 | (Note 12)     |                         |                     |                                              |             |

| 7       | ZXD_DISABLE     |               | -                       |                     | DAC to guarantee immediate mode char         | iges        |

|         |                 | ļ             | waiting for a zero o    | ross. (Note 11)     |                                              |             |

| 8:9     | RSVD            | RESERVE       | ,                       |                     |                                              |             |

| 10:11   | CAP_SIZE        |               |                         |                     | alues to give correct turn-off delay and     |             |

|         |                 | <u> </u>      | erformance. Value is    |                     | · · · ·                                      |             |

|         |                 | 10:11         | Delay                   | Bypass Cap          | bacitor Size                                 |             |

|         |                 | 00            | 25ms                    | 0.1µF               |                                              |             |

|         |                 | 01            | 50ms                    | 0.39µF              |                                              |             |

|         |                 | 10            | 85ms                    | 1µF                 |                                              |             |

|         |                 | 11            | RESERVED                | RESERVED            |                                              |             |

| 12      | ZXDS_SLOW       |               |                         | · ·                 | it for a zero crossing before powering do    | wn          |

| 13      | MUTE_LS         |               | •                       |                     | node where it is not already muted           |             |

| 14      | MUTE_HP         | If set, mute  | s the headphone a       | mplifier in any m   | ode where it is not already muted            |             |

| 14      | MUTE_MIC        | -             | s the microphone p      |                     | ···· <b>,</b> ····                           |             |

# System Control Registers (Continued)

LM4930

# GAIN CONFIG REGISTERS

This register is used to control the gain of the headphone amplifier, the loudspeaker amplifier, and the microphone preamplifier. The 7 bit address for the GAINCONFIG register is XX10010. (X = 0 if ADDR is set to logic 0) (X = 1 if ADDR is set to logic 1)

# GAINCONFIG (XX10010). (Set = logic 1, Clear = logic 0)

| BIT   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| RESET | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Address | Register      | Description | n                      |                       |                    |

|---------|---------------|-------------|------------------------|-----------------------|--------------------|

| 4:0     | LOUDSPKR_GAIN | Programs t  | he gain of the loudspe | aker amplifier. Gain  | is set as follows: |

|         |               | 4:0         | Loudspeaker<br>Gain    | 4:0                   | Loudspeaker Gain   |

|         |               | 00000       | -34.5dB                | 10000                 | -10.5dB            |

|         |               | 00001       | -33dB                  | 10001                 | -9dB               |

|         |               | 00010       | -31.5dB                | 10010                 | -7.5dB             |

|         |               | 00011       | -30dB                  | 10011                 | -6dB               |

|         |               | 00100       | -28.5dB                | 10100                 | -4.5dB             |

|         |               | 00101       | -27dB                  | 10101                 | -3dB               |

|         |               | 00110       | -25.5dB                | 10110                 | -1.5dB             |

|         |               | 00111       | -24dB                  | 10111                 | 0dB                |

|         |               | 01000       | -22.5dB                | 11000                 | 1.5dB              |

|         |               | 01001       | -21dB                  | 11001                 | 3dB                |

|         |               | 01010       | -19.5dB                | 11010                 | 4.5dB              |

|         |               | 01011       | -18dB                  | 11011                 | 6dB                |

|         |               | 01100       | -16.5dB                | 11100                 | 7.5dB              |

|         |               | 01101       | -15dB                  | 11101                 | 9dB                |

|         |               | 01110       | -13.5dB                | 11110                 | 10.5dB             |

|         |               | 01111       | -12dB                  | 11111                 | 12dB               |

| 9:5     | HP_GAIN       | Programs t  | he gain of the headph  | one amplifier. Gain i | s set as follows:  |

|         |               | 9:5         | Headphone Gain         | 9:5                   | Headphone Gain     |

|         |               | 00000       | -46dB                  | 10000                 | -22.5dB            |

|         |               | 00001       | -45dB                  | 10001                 | -21dB              |

|         |               | 00010       | -43.5dB                | 10010                 | -19.5dB            |

|         |               | 00011       | -42db                  | 10011                 | -18dB              |

|         |               | 00100       | -40.5dB                | 10100                 | -16.5dB            |

|         |               | 00101       | -39dB                  | 10101                 | -15dB              |

|         |               | 00110       | -37.5dB                | 10110                 | -13.5dB            |

|         |               | 00111       | -36dB                  | 10111                 | -12dB              |

|         |               | 01000       | -34.5dB                | 11000                 | -10.5dB            |

|         |               | 01001       | -33dB                  | 11001                 | -9dB               |

|         |               | 01010       | -31.5dB                | 11010                 | -7.5dB             |

|         |               | 01011       | -30dB                  | 11011                 | -6dB               |

|         |               | 01100       | -28.5dB                | 11100                 | -4.5dB             |

|         |               | 01101       | -27dB                  | 11101                 | -3dB               |

|         |               | 01110       | -25.5dB                | 11110                 | -1.5dB             |

|         |               | 01111       | -24dB                  | 11111                 | 0dB                |

| 13:10   | MIC_GAIN      | Programs t  | he gain of the microph | one amplifier. Gain   | is set as follows: |

|      |      | GAIN CONFI       | IG REGISTERS (Continued) |  |

|------|------|------------------|--------------------------|--|

|      |      | 13:10            | Mic Preamp Gain          |  |

|      |      | 0000             | 17dB                     |  |

|      |      | 0001             | 19dB                     |  |

|      |      | 0010             | 21dB                     |  |

|      |      | 0011             | 23dB                     |  |

|      |      | 0100             | 25dB                     |  |

|      |      | 0101             | 27dB                     |  |

|      |      | 0110             | 29dB                     |  |

|      |      | 0111             | 31dB                     |  |

|      |      | 1000             | 33dB                     |  |

|      |      | 1001             | 35dB                     |  |

|      |      | 1010             | 37dB                     |  |

|      |      | 1011             | 39dB                     |  |

|      |      | 1100             | 41dB                     |  |

|      |      | 1101             | 43dB                     |  |

|      |      | 1110             | 45dB                     |  |

|      |      | 1111             | 47dB                     |  |

| 5:14 | RSVD | RESERVED (Note 1 | 3)                       |  |

# Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Analog Supply Voltage          | 6.0V               |

|--------------------------------|--------------------|

| Digital Storage Supply Voltage | 6.0V               |

| Storage temperature            | -65°C to +150°C    |

| Power Dissipation (Note 3)     | Internally Limited |

| ESD Susceptibility             |                    |

| Human Body Model (Note 4)      | 2000V              |

| Machine Model (Note 5)         | 200V               |

| Junction temperature           | 150°C              |

|                                |                    |

| Thermal Resistance                 |         |

|------------------------------------|---------|

| θ <sub>JA</sub> - TLA36KRA         | 105°C/W |

| θ <sub>JA</sub> - LQA44A (Note 17) | 27°C/W  |

# **Operating Ratings** (Note 3)

| Temperature Range                 |                                           |

|-----------------------------------|-------------------------------------------|

| $T_{MIN} \leq T_{A} \leq T_{MAX}$ | $-30^{\circ}C \le T_{A} \le +85^{\circ}C$ |

| Supply Voltage                    |                                           |

| DV <sub>DD</sub> (Note 8)         | 2.6V - 4.5V                               |

| AV <sub>DD</sub> (Note 8)         | 2.6V - 5.5V                               |

# Electrical Characteristics $\text{DV}_{\text{DD}}$ = 3.3V, $\text{AV}_{\text{DD}}$ = 5V, $\text{R}_{\text{LHP}}$ = 32 $\Omega,$ $\text{R}_{\text{LHF}}$ = 8 $\Omega$

(Notes 1, 2, 8)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol           | Parameter                                                            | Conditions                                                           | LM4930              |                            | Units     |

|------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|---------------------|----------------------------|-----------|

|                  |                                                                      |                                                                      | Typical<br>(Note 6) | Limits<br>(Notes 7,<br>15) | (Limits)  |

|                  |                                                                      | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0010"                |                     |                            |           |

|                  |                                                                      | Output Mode = "0010"<br>Output Mode = "0011"<br>Output Mode = "0100" | 2                   |                            |           |

| DI <sub>DD</sub> | Digital Power Supply Current                                         | Output Mode = "0101"<br>Output Mode = "0110"<br>Output Mode = "0111" | 4.4                 |                            |           |

|                  | Output Mode = "1000"<br>Output Mode = "1001"<br>Output Mode = "1010" | 4.9                                                                  | 8                   | mA (max)                   |           |

|                  | f <sub>MCLK</sub> = 12.288MHz; No Load                               |                                                                      |                     |                            |           |

|                  |                                                                      | Output Mode = "0010"                                                 | 7.0                 |                            |           |

|                  | Output Mode = "0011"                                                 | 6.3                                                                  |                     |                            |           |

|                  | Output Mode = "0100"                                                 | 8.0                                                                  |                     |                            |           |

|                  | Al <sub>DD</sub> Analog Power Supply Quiescent<br>Current            | Output Mode = "0101"                                                 | 8.2                 |                            |           |

| AI <sub>DD</sub> |                                                                      | Output Mode = "0110"                                                 | 7.4                 |                            |           |

|                  |                                                                      | Output Mode = "0111"                                                 | 8.7                 |                            |           |

|                  |                                                                      | Output Mode = "1000"<br>Output Mode = "1001"<br>Output Mode = "1010" | 9.5                 | 14                         | mA (max)  |

| DI <sub>SD</sub> | Digital Powerdown Current                                            | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0000" Powerdown Mode | 1                   | 7                          | µA (max)  |

| Al <sub>SD</sub> | Analog Powerdown Current                                             | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0000" Powerdown Mode | 1                   | 2                          | μA (max)  |

| DI <sub>ST</sub> | Digital Standby Current                                              | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0001" Standby Mode   | 1.4                 | 2                          | mA (max)  |

| Al <sub>st</sub> | Analog Standby Current                                               | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0001" Standby Mode   | 230                 | 1000                       | µA (max)  |

| $V_{FS\_LS}$     | Full-Scale Output Voltage<br>(Mono speaker amplifier)                | CLASS = 0; 0dB gain setting; 8Ω BTL<br>load (Note 10)                | 2.5                 |                            | $V_{P-P}$ |

| $V_{FS_{HP}}$    | Full-Scale Output Voltage<br>(Headphone amplifier)                   | 0dB gain setting; 32Ω Stereo Load (Note 10)                          | 2.5                 |                            | $V_{P-P}$ |

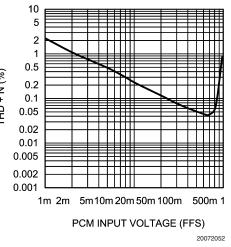

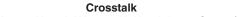

### LM4930 Electrical Characteristics $DV_{DD} = 3.3V$ , $AV_{DD} = 5V$ , $R_{LHP} = 32\Omega$ , $R_{LHF} = 8\Omega$ (Notes 1, 2, 8) (Continued) The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for $T_A = 25^{\circ}C$ . Symbol Parameter Conditions LM4930 Units (Limits) Typical Limits (Note 6) (Notes 7, 15) Mic Bias Voltage 2.0 V V<sub>MIC\_BIAS</sub> THD+N Headphone Amplifier Total $f_{IN} = 1 \text{ kHz}, P_{OUT} = 7.5 \text{mW}; 32 \Omega \text{ Stereo}$ 0.07 % Harmonic Motion Distortion + l oad Noise POHP Headphone Amplifier Output THD+N = 0.5%, $f_{OUT} = 1 \text{kHz}$ 27 20 mW (min) Power 1 POLS Mono Speaker Amplifier Output THD+N = 1%, $f_{OUT} = 1$ kHz W Power $C_{BYPASS} = 1.0 \mu F$ PSRR Power Supply Rejection Ratio 55 45 dB (min) $C_{DAC REF} = 1.0 \mu F$ V<sub>RIPPLE</sub> = 200mV<sub>P-P</sub> @ 217Hz, MIC\_P, MIC\_N terminated with $10\Omega$ to ground SNR Signal-to-Noise Ratio Signal = Vo at f = 1kHz @1% THD+N, 72 dB (Voice DAC Path) (Voice) $32\Omega$ Stereo Load; Noise = digital zero, A-weighted, 0dB gain setting SNR Signal-to-Noise Ratio (Music Signal = Vo at f = 1kHz @1% THD+N, 86 dB (Music) Audio Path) $32\Omega$ Stereo Load; Noise = digital zero, A-weighted; 0dB gain setting DR Dynamic Range (Voice DAC Path) Signal = Vo at f = 1kHz @1% THD+N, 72 dB (Voice) 32Ω Stereo Load; Noise for -60dBFS digital input; A-weighted; 0dB gain setting DR Dynamic Range (Music Audio Signal = Vo at f=1kHz @1% THD+N, 32Ω 86 dB Path) Stereo Load; Noise for -60dBFS digital (Music) input; A-weighted, 0dB gain setting SNR<sub>ADC</sub> Signal-to-Noise Ratio Reference signal = 0dBFS 75 dB (Voice ADC Path) MIC\_P, MIC\_N terminated with 10Ω to ground; A-weighted; 47dB MIC preamp gain setting DRADC Dynamic Range Reference signal = 0dBFS 75 dB (Voice ADC Path) Noise for -60dBFS digital input; A-weighted; 47dB MIC preamp gain setting 75 Stereo Channel-to-Channel f<sub>S</sub> = 48kHz, f<sub>IN</sub> = 1kHz sinewave at dB $X_{\text{TALK}}$ Crosstalk -3dB<sub>FS</sub> Maximum Differential MIC Input 17dB MIC Preamp gain setting V<sub>MIC-IN</sub> 570 $mV_{P-P}$ Voltage

dB (max)

dB (max)

kHz

dB

kHz

300Hz - 3.3kHz through head-phone

300Hz - 3.3kHz through head-phone

output.

output.

-3dB Point

Above 4kHz

Upper -3dB Point

+/-0.15

+/-0.25

3.46

72

3.47

+/-0.2

+/-0.3

$R_{VDAC}$

R<sub>VADC</sub>

$PB_{VDAC}$

SBAVDAC

**UPB**<sub>VADC</sub>

Voice DAC Ripple

Voice ADC Ripple

Cutoff Frequency.

Voice DAC Passband

Voice DAC Stopband Attenuation

Voice ADC Upper Passband

# Electrical Characteristics $\text{DV}_{\text{DD}}$ = 3.3V, $\text{AV}_{\text{DD}}$ = 5V, $\text{R}_{\text{LHP}}$ = 32 $\Omega,$ $\text{R}_{\text{LHF}}$ = 8 $\Omega$

(Notes 1, 2, 8) (Continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol               | Parameter                                         | Conditions                                                                                                | LM4                        | 4930     | Units              |  |

|----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|----------|--------------------|--|

|                      |                                                   | Typical<br>(Note 6)                                                                                       | Limits<br>(Notes 7,<br>15) | (Limits) |                    |  |

| PB <sub>VADC</sub>   | Voice ADC Lower Passband<br>Cutoff Frequency.     | Lower -3dB Point                                                                                          | 0.230                      |          | kHz                |  |

| SBA <sub>VADC</sub>  | Voice ADC Stopband Attenuation                    | Above 4kHz                                                                                                | 65                         |          | dB                 |  |

| SBA <sub>NOTCI</sub> |                                                   | Centered on 55Hz, figure gives worst case attenuation for 50Hz & 60Hz.                                    | 58                         |          | dB                 |  |

| R <sub>DAC</sub>     | Audio DAC Ripple                                  | 20Hz - 20kHz through head-phone output.                                                                   | +/-0.1                     | +/-0.2   | dB (max)           |  |

| PB <sub>DAC</sub>    | Audio DAC Passband Width                          | -3dB point                                                                                                | 22.7                       |          | kHz                |  |

| SBA <sub>DAC</sub>   | Audio DAC Stopband Attenuation                    | Above 24kHz                                                                                               | 76                         |          | dB                 |  |

| DR <sub>DAC</sub>    | Audio DAC Dynamic Range<br>Digital Filter Section | Signal = VO at f = 1kHz @ 1% THD+N;<br>f = 1kHz; Noise for -60dBFS digital input;<br>0dB gain; A-weighted | 97                         |          | dB                 |  |

| SNR <sub>dac</sub>   | Audio DAC SNR Digital Filter<br>Section           | Signal = VO at f = 1kHz @ 1% THD+N;<br>f = 1kHz; Noise for -60dBFS digital input;<br>0dB gain; A-weighted | 97                         |          | dB                 |  |

| ∆A <sub>CH-CH</sub>  | Stereo Channel-to-Channel Gain<br>Mismatch        |                                                                                                           | 0.3                        |          | dB                 |  |

| V <sub>IL</sub>      | Digital Input: Logic Low Voltage<br>Level         |                                                                                                           | 0.4                        |          | V                  |  |

| V <sub>IH</sub>      | Digital Input: Logic High Voltage<br>Level        |                                                                                                           | 1.4                        |          | V                  |  |

|                      | Volume Control Range                              | Maximum Attenuation                                                                                       | -46.5                      |          | dB                 |  |

|                      | (Headphone amplifiers)                            | Minimum Attenuation                                                                                       | 0                          |          | dB                 |  |

|                      | Volume Control Range (Mono                        | Minimum Gain                                                                                              | -34.5                      |          | dB                 |  |

|                      | speaker amplifier)                                | Maximum Gain                                                                                              | 12                         |          | dB                 |  |

|                      | Volume Control Step Size (Output amplifiers)      |                                                                                                           | 1.5                        |          | dB                 |  |

|                      | Volume Control Range                              | Minimum Gain                                                                                              | 17                         |          | dB                 |  |

|                      | (Microphone Preamp)                               | Maximum Gain                                                                                              | 47                         |          | dB                 |  |

|                      | Volume Control Step Size<br>(Microphone Preamp)   |                                                                                                           | 2                          |          | dB                 |  |

|                      | Side Tone Attenuation Range                       | Maximum Attenuation<br>Minimum Attenuation                                                                | -30<br>0                   |          | dB<br>dB           |  |

|                      | Side Tone Attenuation Step Size                   |                                                                                                           | 3                          |          | dB                 |  |

| MCLK                 | MCLK frequency                                    | CLOCK_DIV = 0                                                                                             | 12.288                     |          | MHz                |  |

|                      |                                                   | CLOCK_DIV = 1                                                                                             | 24.576                     |          | MHz                |  |

|                      | MCLK Duty Cycle                                   |                                                                                                           | 50                         | 40<br>60 | % (min)<br>% (max) |  |

| CONV                 | Sampling Clock Frequency (Note 9)                 |                                                                                                           | 48                         |          | kHz                |  |

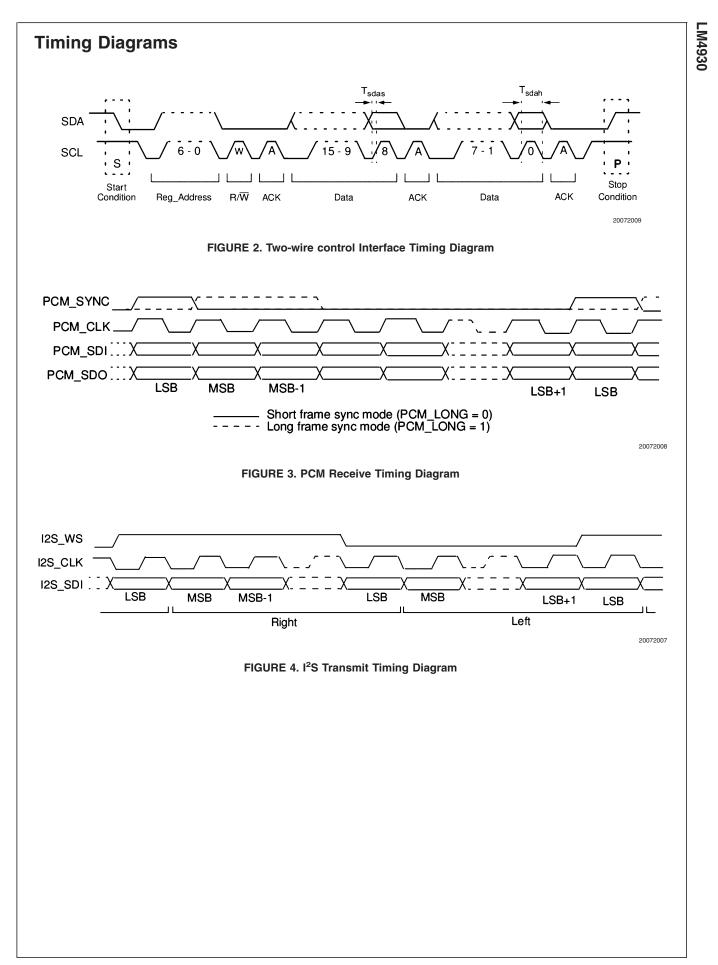

| CLKSCL               | SCL_CLK Frequency                                 |                                                                                                           | 400                        |          | kHz                |  |

| RISESCL              | SCL_CLK, SCL_DATA Rise Time                       |                                                                                                           | 300                        |          | ns                 |  |

| FALLSCL              | SCL_CLK, SDA_DATA Fall Time                       |                                                                                                           | 300                        |          | ns                 |  |

| SDAH                 | SDA_DATA Hold Time                                |                                                                                                           | 500                        |          | ns                 |  |

| SDAN                 | SDA_DATA Setup Time                               |                                                                                                           | 500                        |          | ns                 |  |

# Electrical Characteristics $DV_{DD}$ = 3.3V, $AV_{DD}$ = 5V, $R_{LHP}$ = 32 $\Omega$ , $R_{LHF}$ = 8 $\Omega$

(Notes 1, 2, 8) (Continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol              | Parameter Conditions LM4930 |                    | 930      | Units     |          |

|---------------------|-----------------------------|--------------------|----------|-----------|----------|

|                     |                             |                    | Typical  | Limits    | (Limits) |

|                     |                             |                    | (Note 6) | (Notes 7, |          |

|                     |                             |                    |          | 15)       |          |

|                     |                             | PCM SYNC MODE - 00 | 128      |           | kHz      |

| f <sub>CLKPCM</sub> | PCM_CLK Frequency           | PCM_SYNC_MODE = 00 | -        |           | KIIZ     |

|                     |                             | PCM_SYNC_MODE = 01 | 256      |           |          |

|                     |                             | PCM_SYNC_MODE = 10 | 512      |           |          |

|                     | PCM_CLK Duty Cycle          |                    | 50       | 40        | % (min)  |

|                     |                             |                    |          | 60        | % (max)  |

| f <sub>CLKI2S</sub> | I2S_CLK Frequency           | I2S_RES = 0        | 1.536    |           | MHz      |

|                     |                             | I2S_RES = 1        | 3.072    |           |          |

|                     | I2S_CLK Duty Cycle          |                    | 50       | 40        | % (min)  |

|                     |                             |                    |          | 60        | % (max)  |

# Electrical Characteristics $DV_{DD} = 3V$ , $AV_{DD} = 3V$ , $R_{LHP} = 32\Omega$ , $R_{LHF} = 8\Omega$

(Notes 1, 2, 3)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol Parameter | Parameter Conditions                   |                                     | LM4                 | Units                      |            |

|------------------|----------------------------------------|-------------------------------------|---------------------|----------------------------|------------|

|                  |                                        |                                     | Typical<br>(Note 6) | Limits<br>(Notes 7,<br>15) | (Limits)   |

|                  |                                        | f <sub>MCLK</sub> = 12.288MHz       |                     |                            |            |

|                  |                                        | Output Mode = "0010"                |                     |                            |            |

|                  |                                        | Output Mode = "0011"                | 1.6                 |                            |            |

|                  |                                        | Output Mode = "0100"                |                     |                            |            |

| DI <sub>DD</sub> | Digital Power Supply Current           | Output Mode = "0101"                |                     |                            |            |

| DIDD             | Digital i owel Supply Surrent          | Output Mode = "0110"                | 3.8                 |                            |            |

|                  |                                        | Output Mode = "0111"                |                     |                            |            |

|                  |                                        | Output Mode = "1000"                |                     |                            |            |

|                  |                                        | Output Mode = "1001"                | 4.2                 | 7                          | mA (max)   |

|                  |                                        | Output Mode = "1010"                |                     |                            |            |

|                  | f <sub>MCLK</sub> = 12.288MHz; No Load |                                     |                     |                            |            |

|                  |                                        | Output Mode = "0010"                | 5.8                 |                            |            |

|                  |                                        | Output Mode = "0011"                | 5.1                 |                            |            |

|                  |                                        | Output Mode = "0100"                | 6.5                 |                            |            |

| A 1              | Analog Power Supply Quiescent          | Output Mode = "0101"                | 6.4                 |                            |            |

| Al <sub>DD</sub> | Current                                | Output Mode = "0110"                | 5.8                 |                            |            |

|                  |                                        | Output Mode = "0111"                | 7.0                 |                            |            |

|                  |                                        | Output Mode = "1000"                |                     |                            |            |

|                  |                                        | Output Mode = "1001"                | 7.5                 | 12                         | mA (max)   |

|                  |                                        | Output Mode = "1010"                |                     |                            |            |

| DI <sub>SD</sub> | Digital Powerdown Current              | f <sub>MCLK</sub> = 12.288MHz       | 1                   | 7                          | µA (max)   |

|                  |                                        | Output Mode = "0000" Powerdown Mode |                     |                            | ,          |

| Alsd             | Analog Powerdown Current               | f <sub>MCLK</sub> = 12.288MHz       | 0.0                 | 4.5                        |            |

|                  |                                        | Output Mode = "0000" Powerdown Mode | 0.6                 | 1.5                        | µA (max)   |

| DI <sub>ST</sub> | Digital Standby Current                | f <sub>MCLK</sub> = 12.288MHz       |                     | 17                         | m ( m = v) |

|                  |                                        | Output Mode = "0001" Standby Mode   | 1.1                 | 1.7                        | mA (max)   |

# Electrical Characteristics $\text{DV}_{\text{DD}}$ = 3V, $\text{AV}_{\text{DD}}$ = 3V, $\text{R}_{\text{LHP}}$ = 32 $\Omega,$ $\text{R}_{\text{LHF}}$ = 8 $\Omega$

(Notes 1, 2, 3) (Continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol Parameter               | Parameter                                                | Conditions                                                                                                                      | LM                         | 4930     | Units             |

|--------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|-------------------|

|                                |                                                          | Typical<br>(Note 6)                                                                                                             | Limits<br>(Notes 7,<br>15) | (Limits) |                   |

| AI <sub>st</sub>               | Analog Standby Current                                   | f <sub>MCLK</sub> = 12.288MHz<br>Output Mode = "0001" Standby Mode                                                              | 100                        | 300      | μA (max)          |

| V <sub>FS_LS</sub>             | Full-Scale Output Voltage<br>(Mono speaker amplifier)    | CLASS = 0; 0dB gain setting; $8\Omega$ BTL load (Note 10)                                                                       | 2.5                        |          | $V_{P-P}$         |

| V <sub>FS_HP</sub>             | Full-Scale Output Voltage<br>(Headphone amplifier)       | 0dB gain setting; 32Ω Stereo Load (Note<br>10)                                                                                  | 2.5                        |          | V <sub>P-P</sub>  |

| /                              | Mic Bias Voltage                                         |                                                                                                                                 | 2                          |          | V                 |

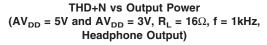

| V <sub>MIC_BIAS</sub><br>THD+N | Headphone Amplifier Total<br>Harmonic Distortion + Noise | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> = 7.5mW                                                                                | 0.07                       |          | %                 |

| Ронр                           | Headphone Amplifier Output<br>Power                      | THD+N = 0.5%, f <sub>OUT</sub> = 1kHz                                                                                           | 25                         | 15       | mW (min)          |

| P <sub>OLS</sub>               | Mono Speaker Amplifier Output<br>Power                   | THD+N = 1%, f <sub>OUT</sub> = 1kHz                                                                                             | 330                        | 270      | mW (min)          |

| PSRR                           | Power Supply Rejection Ratio                             | $C_{BYPASS} = 1.0\mu F$<br>$C_{DAC_REF} = 1.0\mu F$<br>$V_{RIPPLE} = 200mV_{P-P} @ 217Hz$                                       | 50                         | 42       | dB (min)          |

| SNR<br>(Voice)                 | Signal-to-Noise Ratio<br>(Voice DAC Path)                | Signal = Vo at f = 1kHz @1% THD+N,<br>32Ω Stereo Load; Noise = digital zero,<br>A-weighted; 0dB gain setting                    | 72                         |          | dB                |

| SNR<br>(Music)                 | Signal-to-Noise Ratio (Music<br>Audio Path)              | Signal = Vo at f = 1kHz @1% THD+N,<br>32Ω Stereo Load; Noise = digital zero,<br>A-weighted; 0dB gain setting                    | 86                         |          | dB                |

| DR<br>(Voice)                  | Dynamic Range (Voice DAC Path)                           | Signal = Vo at f = 1kHz @1% THD+N,<br>32 $\Omega$ Stereo Load; Noise for -60dBFS<br>digital input; A-weighted, 0dB gain setting | 72                         |          | dB                |

| DR<br>(Music)                  | Dynamic Range (Music Audio<br>Path)                      | Signal = Vo at f=1kHz @1% THD+N, 32Ω<br>Stereo Load; Noise for -60dBFS digital<br>input; A-weighted, 0dB gain setting           | 86                         |          | dB                |

| SNR <sub>ADC</sub>             | Signal-to-Noise Ratio<br>(Voice ADC Path)                | Reference signal = 0dBFS<br>MIC_P, MIC_N terminated with 10Ω to<br>ground;<br>A-weighted; 47dB MIC preamp gain<br>setting       | 75                         |          | dB                |

| DR <sub>ADC</sub>              | Dynamic Range<br>(Voice ADC Path)                        | Reference signal = 0dBFS<br>Noise for -60dBFS digital input;<br>A-weighted; 47dB MIC preamp gain<br>setting                     | 75                         |          | dB                |

| X <sub>TALK</sub>              | Stereo Channel-to-Channel<br>Crosstalk                   | $f_{S} = 48$ kHz, $f_{IN} = 1$ kHz sinewave at<br>-3dB <sub>FS</sub>                                                            | 73                         |          | dB                |

| V <sub>MIC-IN</sub>            | Maximum Differential MIC Input<br>Voltage                | 17dB MIC Preamp gain setting                                                                                                    | 570                        |          | mV <sub>P-P</sub> |

| R <sub>VDAC</sub>              | Voice DAC Ripple                                         | 300Hz - 3.3kHz through head-phone output.                                                                                       | +/-0.15                    | +/-0.2   | dB (max)          |

| R <sub>VADC</sub>              | Voice ADC Ripple                                         | 300Hz - 3.3kHz through head-phone output.                                                                                       | +/-0.25                    | +/-0.3   | dB (max)          |

| PB <sub>VDAC</sub>             | Voice DAC Passband                                       | -3dB Point                                                                                                                      | 3.46                       |          | kHz               |

# Electrical Characteristics $DV_{DD} = 3V$ , $AV_{DD} = 3V$ , $R_{LHP} = 32\Omega$ , $R_{LHF} = 8\Omega$

(Notes 1, 2, 3) (Continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for  $T_A=25^{\circ}C$ .

| Symbol               | Parameter                                                              | Conditions                                                                                                | LM4                 | 4930                       | Units              |

|----------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------------|--------------------|

|                      |                                                                        |                                                                                                           | Typical<br>(Note 6) | Limits<br>(Notes 7,<br>15) | (Limits)           |

| SBA <sub>VDAC</sub>  | Voice DAC Stopband Attenuation                                         | Above 4kHz                                                                                                | 72                  |                            | dB                 |

| UPB <sub>VADC</sub>  | Voice ADC Upper Passband<br>Cutoff Frequency.                          | Upper -3dB Point                                                                                          | 3.47                |                            | kHz                |

| LPB <sub>VADC</sub>  | Voice ADC Lower Passband<br>Cutoff Frequency.                          | Lower -3dB Point                                                                                          | 0.230               |                            | kHz                |

| SBA <sub>VADC</sub>  | Voice ADC Stopband Attenuation                                         | Above 4kHz                                                                                                | 65                  |                            | dB                 |

| SBA <sub>NOTCH</sub> | Voice ADC Notch Attenuation                                            | Centered on 55Hz, figure gives worst case attenuation for 50Hz & 60Hz.                                    | 58                  |                            | dB                 |

| R <sub>DAC</sub>     | Audio DAC Ripple                                                       | 20Hz - 20kHz through head-phone output.                                                                   | +/-0.1              | +/-0.2                     | dB (max)           |

| PB <sub>DAC</sub>    | Audio DAC Passband Width                                               | -3dB point                                                                                                | 22.7                |                            | kHz                |

| SBA <sub>DAC</sub>   | Audio DAC Stopband Attenuation                                         | Above 24kHz                                                                                               | 76                  |                            | dB                 |

| DR <sub>DAC</sub>    | Audio DAC Dynamic Range<br>Digital Filter Section                      | Signal = VO at f = 1kHz @ 1% THD+N;<br>f = 1kHz; Noise for -60dBFS digital input;<br>0dB gain; A-weighted | 97                  |                            | dB                 |

| SNR <sub>DAC</sub>   | Audio DAC SNR Digital Filter<br>Section                                | Signal = VO at f = 1kHz @ 1% THD+N;<br>f = 1kHz; Noise for -60dBFS digital input;<br>0dB gain; A-weighted | 97                  |                            | dB                 |

| $\Delta A_{CH-CH}$   | Stereo Channel-to-Channel Gain<br>Mismatch                             |                                                                                                           | 0.3                 |                            | dB                 |

| V <sub>IL</sub>      | Digital Input: Logic Low Voltage<br>Level                              |                                                                                                           | 0.4                 |                            | V                  |

| V <sub>IH</sub>      | Digital Input: Logic High Voltage<br>Level                             |                                                                                                           | 1.4                 |                            | V                  |

|                      | Volume Control Range                                                   | Maximum Attenuation                                                                                       | -46.5               |                            | dB                 |

|                      | (Headphone amplifiers)                                                 | Minimum Attenuation                                                                                       | 0                   |                            | dB                 |

|                      | Volume Control Range (Mono                                             | Minimum Gain                                                                                              | -34.5               |                            | dB                 |

|                      | speaker amplifier)                                                     | Maximum Gain                                                                                              | 12                  |                            | dB                 |

|                      | Volume Control Step Size (Output amplifiers)                           |                                                                                                           | 1.5                 |                            | dB                 |

|                      | Volume Control Range                                                   | Minimum Gain                                                                                              | 17                  |                            | dB                 |

|                      | (Microphone Preamp)<br>Volume Control Step Size<br>(Microphone Preamp) | Maximum Gain                                                                                              | 47<br>2             |                            | dB                 |

|                      | Side Tone Attenuation Range                                            | Maximum Attenuation<br>Minimum Attenuation                                                                | -30<br>0            |                            | dB<br>dB           |

|                      | Side Tone Attenuation Step Size                                        |                                                                                                           | 3                   |                            | dB                 |

| f <sub>MCLK</sub>    | MCLK frequency                                                         | CLOCK_DIV = 0                                                                                             | 12.288              |                            | MHz                |

|                      |                                                                        | CLOCK_DIV = 1                                                                                             | 24.576              |                            | MHz                |

|                      | MCLK Duty Cycle                                                        |                                                                                                           | 50                  | 40<br>60                   | % (min)<br>% (max) |

| f <sub>CONV</sub>    | Sampling Clock Frequency                                               | (Note 9)                                                                                                  | 48                  |                            | kHz                |

| CLKSCL               | SCL_CLK Frequency                                                      |                                                                                                           | 400                 |                            | kHz                |

| t <sub>RISESCL</sub> | SCL_CLK, SCL_DATA Rise Time                                            |                                                                                                           | 300                 |                            | ns                 |

| t <sub>fallscl</sub> | SCL_CLK, SDA_DATA Fall Time                                            |                                                                                                           | 300                 |                            | ns                 |

| t <sub>sdah</sub>    | SDA_DATA Hold Time                                                     |                                                                                                           | 500                 |                            | ns                 |

# Electrical Characteristics $DV_{DD}$ = 3V, $AV_{DD}$ = 3V, $R_{LHP}$ = 32 $\Omega$ , $R_{LHF}$ = 8 $\Omega$

(Notes 1, 2, 3) (Continued)

The following specifications apply for the circuit shown in Figure 1, unless otherwise specified. Limits apply for T<sub>A</sub>= 25°C.

| Symbol              | Parameter           | Conditions         | LM4                 | 1930                       | Units    |

|---------------------|---------------------|--------------------|---------------------|----------------------------|----------|

|                     |                     |                    | Typical<br>(Note 6) | Limits<br>(Notes 7,<br>15) | (Limits) |

| t <sub>SDAS</sub>   | SDA_DATA Setup Time |                    | 500                 |                            | ns       |

| f <sub>CLKPCM</sub> | PCM_CLK Frequency   | PCM_SYNC_MODE = 00 | 128                 |                            | kHz      |

|                     |                     | PCM_SYNC_MODE = 01 | 256                 |                            | kHz      |

|                     |                     | PCM_SYNC_MODE = 10 | 512                 |                            | kHz      |

|                     | PCM CLK Duty Cycle  |                    | 50                  | 40                         | % (min)  |

|                     | PCM_CLK Duty Cycle  |                    | 50                  | 60                         | % (max)  |

| CLKI2S              | I2S_CLK Frequency   | I2S_RES = 0        | 1.536               |                            | MHz      |

|                     |                     | I2S_RES = 1        | 3.072               |                            | MHz      |

|                     | 100 CLK Duty Cycle  |                    | 50                  | 40                         | % (min)  |

|                     | I2S_CLK Duty Cycle  |                    | 50                  | 60                         | % (max)  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 2: All voltages are measured with respect to the relevant GND pin unless otherwise specified.

**Note 3:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4930, see power derating currents for more information.

**Note 4:** Human body model: 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine model: 220pF - 240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

**Note 8:** Best operation is achieved by maintaining  $3.0V \le AV_{DD} \le 5.0$  and  $3.0V \le DV_{DD} \le 3.6V$ . AV<sub>DD</sub> must be equal to or greater than DV<sub>DD</sub>. for proper operation. **Note 9:** The sampling clock frequency is equal to the master clock frequency divided by 256. ( $f_{conv} = f_{MCLK}/256$ )

Note 10: This value represents the 0dB output level of the given amplifier for the given analog supply voltage. Gain values given in the GAINCONFIG register are relative to these full-scale values for each output amplifier.

Note 11: To ensure a successful transistion into Powerdown Mode, ZXD\_DISABLE must be set whenever there is no audio input signal present.

Note 12: It is recommended to alter this bit only while the part is in Powerdown Mode.

Note 13: Reserved bits should be set to zero when programming the associated register.

Note 14: With the exception of Standby Mode, rapid switching between modes should be avoided. Rapid switching between modes will not ensure that the desired mode will be activated.

Note 15: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

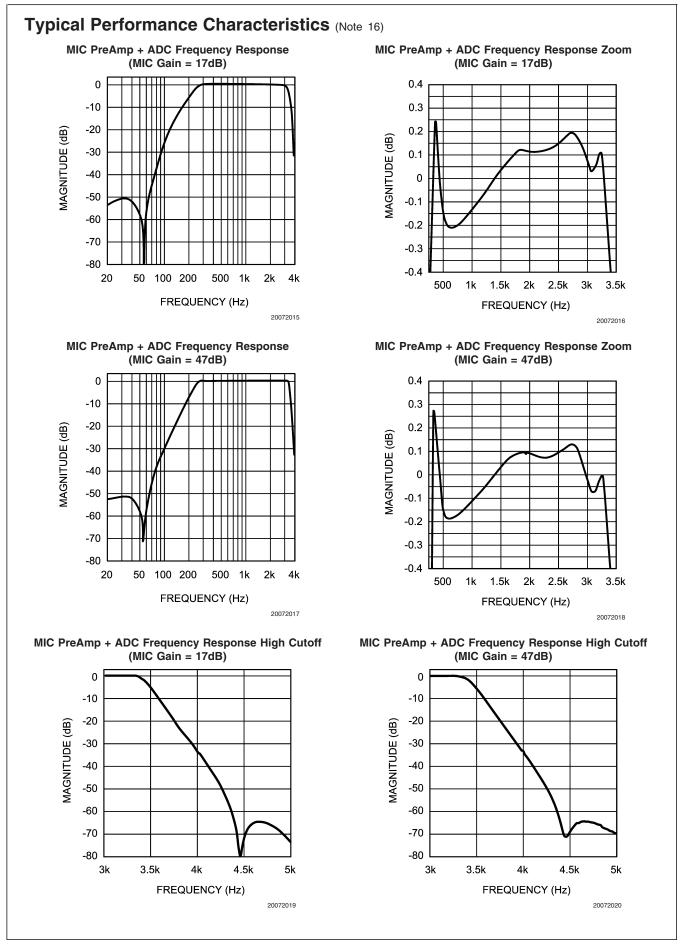

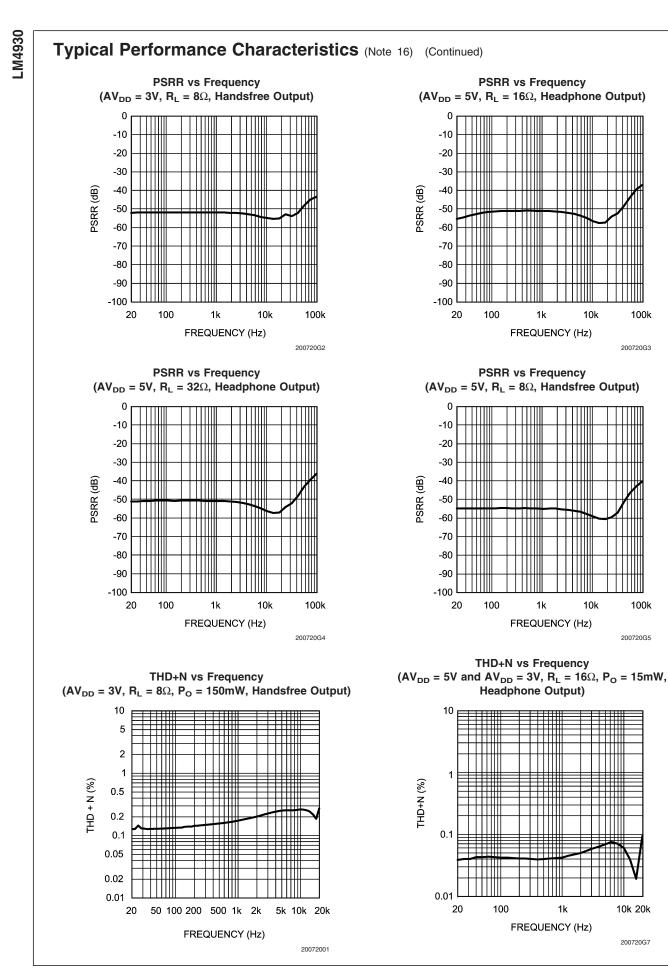

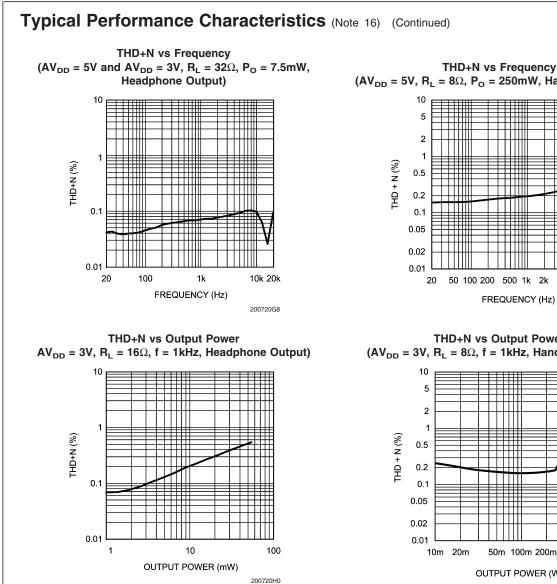

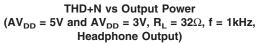

Note 16: 0dBm0 = -3dBFS for the PCM voice codec and 0dBm0 = -1dBFS for the I<sup>2</sup>S DAC, unless otherwise specified.

**Note 17:** The given  $\theta_A$  is for an LM4930 packaged in an LQA44A with the Exposed-DAP soldered to an exposed 2in<sup>2</sup> area of 1oz printed circuit board copper with 16 thermal vias as described in National AN-1187.

www.national.com

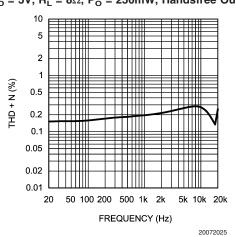

(AV<sub>DD</sub> = 5V, R<sub>L</sub> = 8 $\Omega$ , P<sub>O</sub> = 250mW, Handsfree Output)

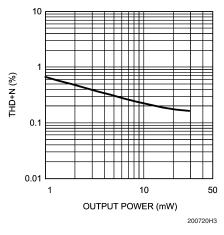

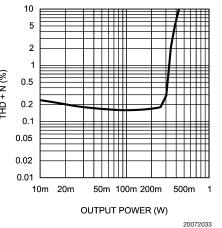

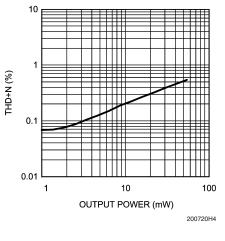

**THD+N vs Output Power**  $(AV_{DD} = 3V, R_{L} = 8\Omega, f = 1kHz, Handsfree Output)$

23