### LM4923 Boomer® Audio Power Amplifier Series

# 1.1 Watt Fully Differential Audio Power Amplifier With Shutdown Select

### **General Description**

The LM4923 is a fully differential audio power amplifier primarily designed for demanding applications in mobile phones and other portable communication device applications. It is capable of delivering 1.1 watt of continuous average power to an  $8\Omega$  BTL load with less than 1% distortion (THD+N) from a  $5V_{DC}$  power supply.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4923 does not require output coupling capacitors or bootstrap capacitors, and therefore is ideally suited for mobile phone and other low voltage applications where minimal power consumption is a primary requirement.

The LM4923 features a low-power consumption shutdown mode. To facilitate this, Shutdown may be enabled by logic low. Additionally, the LM4923 features an internal thermal shutdown protection mechanism.

The LM4923 contains advanced pop & click circuitry which eliminates noises which would otherwise occur during turn-on and turn-off transitions.

### **Key Specifications**

■ Improved PSRR at 217Hz

85dB(typ)

■ Power Output at 5.0V @ 1% THD+N

1.1W(typ)

■ Power Output at 3.3V @ 1% THD+N

400mW(typ)

■ Shutdown Current

0.1µA(typ)

#### **Features**

- Fully differential amplification

- Available in space-saving LLP package

- Ultra low current shutdown mode

- Can drive capacitive loads up to 100pF

- Improved pop & click circuitry eliminates noises during turn-on and turn-off transitions

- 2.4 5.5V operation

- No output coupling capacitors, snubber networks or bootstrap capacitors required

### **Applications**

- Mobile phones

- PDAs

- Portable electronic devices

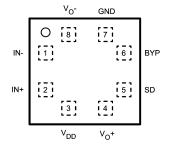

### **Connection Diagrams**

#### LQ Package

Top View Order Number LM4923LQ See NS Package Number LQB08A 8 Pin LQ Marking

20071302

X - Date Code TT - Die Traceability G - Boomer B2 - LM4923LQ

Boomer® is a registered trademark of National Semiconductor Corporation.

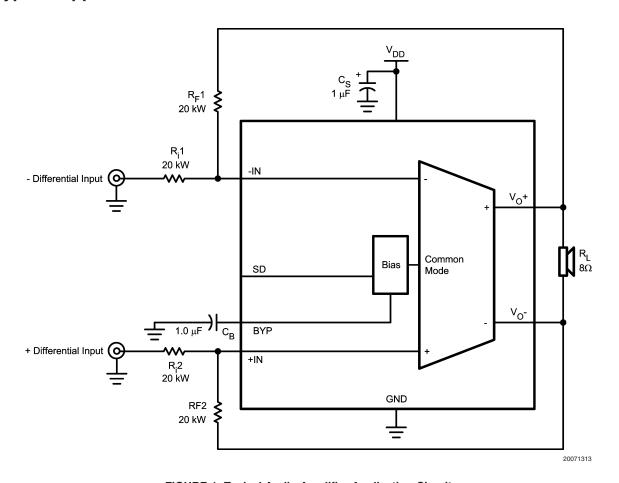

## **Typical Application**

FIGURE 1. Typical Audio Amplifier Application Circuit

### **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 6.0V Storage Temperature -65°C to +150°C Input Voltage -0.3V to  $V_{DD}$  +0.3V Power Dissipation (Note 3) Internally Limited ESD Susceptibility (Note 4) 2000V ESD Susceptibility (Note 5) 200V

Junction Temperature

Thermal Resistance 140°C/W  $\theta_{\mathsf{JA}}$  (LLP) Soldering Information See AN-1187

### **Operating Ratings**

Temperature Range

$-40^{\circ}C \leq T_A \leq 85^{\circ}C$  $T_{MIN} \leq T_A \leq T_{MAX}$ Supply Voltage  $2.4V \leq V_{DD} \leq 5.5V$

Electrical Characteristics  $V_{DD} = 5V$  (Notes 1, 2) The following specifications apply for  $V_{DD} = 5V$ ,  $A_V = 1$ , and  $8\Omega$  load unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

150°C

|                   |                                 |                                            | LM4923   |          |          |  |

|-------------------|---------------------------------|--------------------------------------------|----------|----------|----------|--|

| Symbol            | Parameter                       | Conditions                                 | Typical  | Limit    | Units    |  |

|                   |                                 |                                            | (Note 6) | (Note 7) | (Limits) |  |

| I <sub>DD</sub>   | Quiescent Power Supply Current  | V <sub>IN</sub> = 0V, no load              | 4        | 9        | mA (may) |  |

|                   |                                 | $V_{IN} = 0V, R_L = 8\Omega$               | 4        | 9        | mA (max) |  |

| I <sub>SD</sub>   | Shutdown Current                | V <sub>SHUTDOWN</sub> = GND                | 0.1      | 1        | μA (max) |  |

| P <sub>o</sub>    | Output Power                    | THD = 1% (max); f = 1 kHz                  |          |          |          |  |

|                   |                                 | LM4923, $R_L = 8\Omega$                    | 1.1      | 1        |          |  |

| THD+N             | Total Harmonic Distortion+Noise | $P_o = 0.4 \text{ Wrms}; f = 1 \text{kHz}$ | 0.02     |          | %        |  |

| PSRR              | Power Supply Rejection Ratio    | V <sub>ripple</sub> = 200mV sine p-p       |          |          |          |  |

|                   |                                 | f = 217Hz (Note 8)                         | 85       | 73       |          |  |

|                   |                                 | f = 1kHz (Note 8)                          | 85       | 73       |          |  |

| CMRR              | Common_Mode Rejection Ratio     | f = 217Hz,                                 | 50       |          | dB       |  |

|                   |                                 | $V_{CM} = 200 \text{mV}_{pp}$              |          |          |          |  |

| Vos               | Output Offset                   | $V_{IN} = 0V$                              | 4        |          | mV       |  |

| V <sub>SDIH</sub> | Shutdown Voltage Input High     |                                            | 0.9      |          | V        |  |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low      |                                            | 0.7      |          | V        |  |

Electrical Characteristics  $V_{DD}=3V$  (Notes 1, 2) The following specifications apply for  $V_{DD}=3V$ ,  $A_{V}=1$ , and  $8\Omega$  load unless otherwise specified. Limits apply for  $T_{A}=25^{\circ}C$ .

| Symbol            | Parameter                       | Conditions                                          | LM4923   |          |           |

|-------------------|---------------------------------|-----------------------------------------------------|----------|----------|-----------|

|                   |                                 |                                                     | Typical  | Limit    | Units     |

|                   |                                 |                                                     | (Note 6) | (Note 7) | (Limits)  |

| I <sub>DD</sub>   | Quiescent Power Supply Current  | V <sub>IN</sub> = 0V, no load                       | 3        | 5.5      | m A (max) |

|                   |                                 | $V_{IN} = 0V, R_L = 8\Omega$                        | 3        | 5.5      | mA (max)  |

| I <sub>SD</sub>   | Shutdown Current                | V <sub>SHUTDOWN</sub> = GND                         | 0.1      | 1        | μA (max)  |

| P <sub>o</sub>    | Output Power                    | THD = 1% (max); f = 1kHz<br>LM4923, $R_1 = 8\Omega$ | 0.375    |          | W         |

| THD+N             | Total Harmonic Distortion+Noise | $P_o = 0.25$ Wrms; $f = 1$ kHz                      | 0.02     |          | %         |

| PSRR              | Power Supply Rejection Ratio    | V <sub>ripple</sub> = 200mV sine p-p                |          |          |           |

|                   |                                 | f = 217Hz (Note 8)                                  | 85       |          |           |

|                   |                                 | f = 1kHz (Note 8)                                   | 85       | 73       | 1         |

| CMRR              | Common-Mode Rejection Ratio     | f = 217Hz                                           | 50       |          | dB        |

|                   |                                 | $V_{CM} = 200 \text{mV}_{pp}$                       |          |          |           |

| V <sub>os</sub>   | Output Offset                   | V <sub>IN</sub> = 0V                                | 4        |          | mV        |

| V <sub>SDIH</sub> | Shutdown Voltage Input High     |                                                     | 0.8      |          | V         |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low      |                                                     | 0.6      |          | V         |

Electrical Characteristics  $V_{DD}=3V$  (Notes 1, 2) The following specifications apply for  $V_{DD}=3V$ ,  $A_{V}=1$ , and  $8\Omega$  load unless otherwise specified. Limits apply for  $T_{A}=1$ 25°C. (Continued)

Note 1: All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

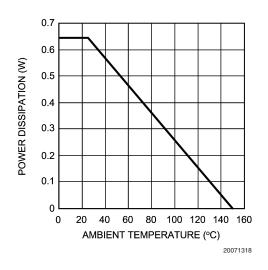

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4923, see power derating curve for additional information.

**Note 4:** Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine Model, 220pF - 240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 8:  $10\Omega$  terminated input.

### **External Components Description**

| Components |                | Functional Description                                                                                                                                                                                      |  |  |

|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.         | R <sub>i</sub> | Inverting input resistance which sets the closed-loop gain in conjunction with R <sub>f</sub> .                                                                                                             |  |  |

| 2.         | R <sub>f</sub> | Feedback resistance which sets the closed-loop gain in conjunction with R <sub>i</sub> .                                                                                                                    |  |  |

| 3.         | Cs             | Supply bypass capacitor which provides power supply filtering. Refer to the <b>Power Supply Bypassing</b> section for information concerning proper placement and selection of the supply bypass capacitor. |  |  |

| 4.         | Св             | Bypass pin capacitor which provides half-supply filtering. Refer to the section, <b>Proper Selection of External Components</b> , for information concerning proper placement and selection of $C_B$ .      |  |  |

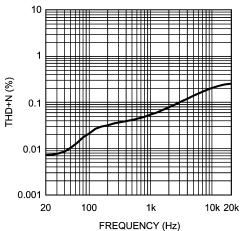

### **Typical Performance Characteristics**

20071306

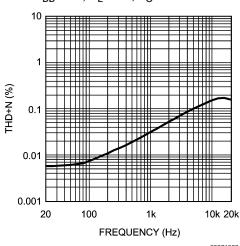

#### THD+N vs Frequency $V_{DD}$ = 2.6V, $R_L$ = $4\Omega$ , $P_O$ = 150mW

20071305

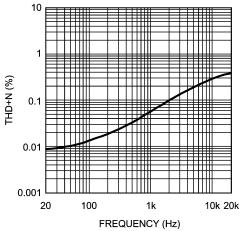

THD+N vs Frequency  $V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ ,  $P_O$  = 400mW

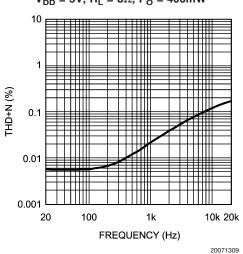

THD+N vs Frequency  $V_{DD} = 3V, R_{L} = 8\Omega, P_{O} = 275mW$

20071308

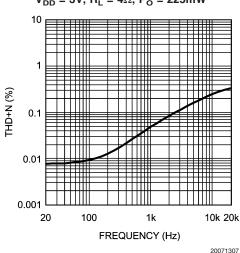

THD+N vs Frequency  $V_{DD} = 3V$ ,  $R_L = 4\Omega$ ,  $P_O = 225$ mW

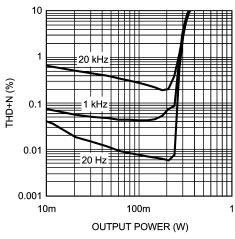

THD+N vs Output Power  $V_{DD} = 2.6V, R_L = 8\Omega$

THD+N vs Output Power  $V_{DD}$  = 2.6V,  $R_L$  =  $4\Omega$

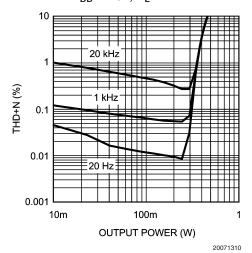

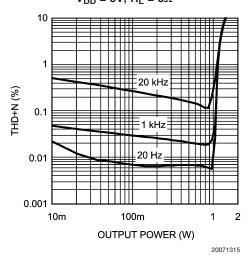

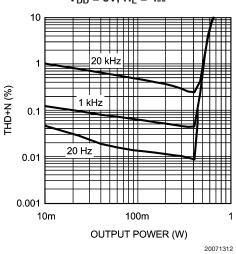

THD+N vs Output Power  $V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$

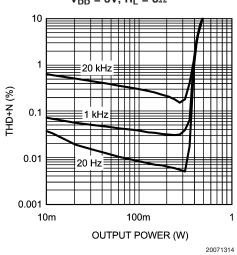

THD+N vs Output Power  $V_{DD} = 3V$ ,  $R_L = 8\Omega$

THD+N vs Output Power  $V_{DD} = 3V$ ,  $R_L = 4\Omega$

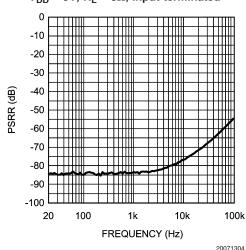

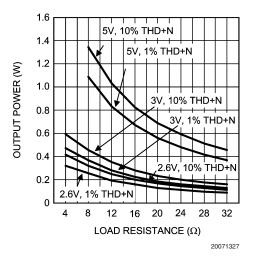

PSRR vs Frequency  $V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ , Input terminated

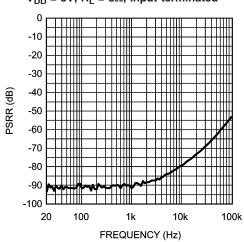

$\label{eq:vdd} \mbox{PSRR vs Frequency} \\ \mbox{V}_{\mbox{DD}} = \mbox{3V}, \mbox{ R}_{\mbox{L}} = \mbox{8}\Omega, \mbox{ Input terminated}$

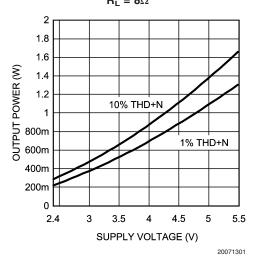

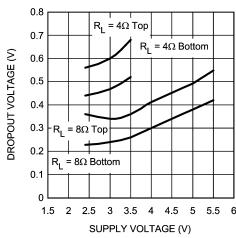

## Output Power vs Supply Voltage $\mathbf{R_L} = \mathbf{8}\Omega$

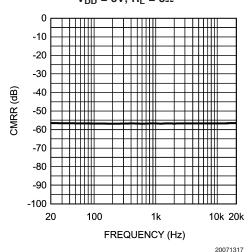

## CMRR vs Frequency $V_{DD}$ = 5V, $R_L$ = 8 $\Omega$

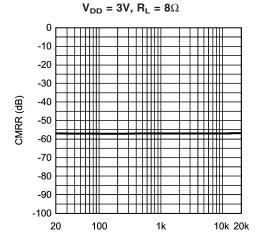

### **CMRR** vs Frequency

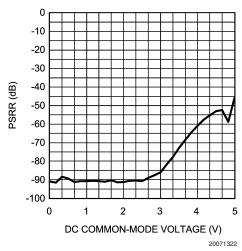

PSRR vs Common Mode Voltage  $V_{DD} = 3V$ ,  $R_L = 8\Omega$ , f = 217Hz

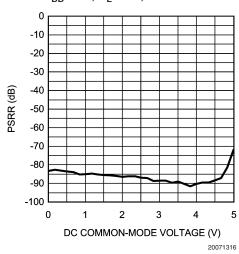

PSRR vs Common Mode Voltage  $V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ , f = 217Hz

FREQUENCY (Hz)

20071326

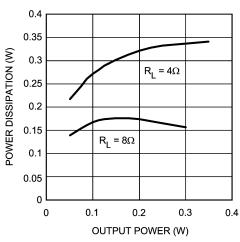

Power Dissipation vs Output Power V<sub>DD</sub> = 2.6V, R<sub>L</sub> = 8 $\Omega$  and 4 $\Omega$

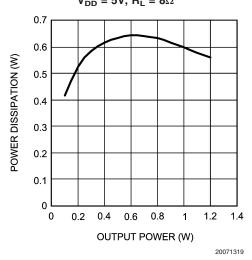

Power Dissipation vs Output Power  $V_{DD}$  = 5V,  $R_L$  =  $8\Omega$

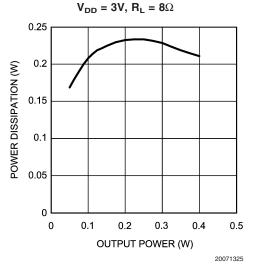

Power Dissipation vs Output Power

**Power Derating Curve**

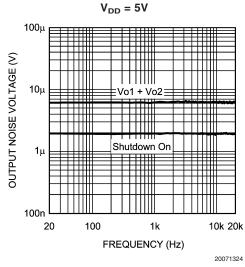

Noise Floor

Noise Floor V<sub>DD</sub> = 3V

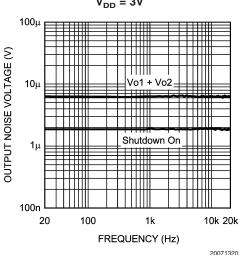

Clipping Voltage vs Supply Voltage

20071323

www.national.com

#### **Output Power vs Load Resistance**

### **Application Information**

#### **DIFFERENTIAL AMPLIFIER EXPLANATION**

The LM4923 is a fully differential audio amplifier that features differential input and output stages. Internally this is accomplished by two circuits: a differential amplifier and a common mode feedback amplifier that adjusts the output voltages so that the average value remains  $V_{\rm DD}$  / 2. When setting the differential gain, the amplifier can be considered to have "halves". Each half uses an input and feedback resistor ( $R_{\rm i1}$  and  $R_{\rm F1}$ ) to set its respective closed-loop gain (see Figure 1). With  $R_{\rm i1}=R_{\rm i2}$  and  $R_{\rm F1}=R_{\rm F2}$ , the gain is set at - $R_{\rm F}$  /  $R_{\rm i}$  for each half. This results in a differential gain of

$$A_{VD} = -R_F/R_i \tag{1}$$

It is extremely important to match the input resistors to each other, as well as the feedback resistors to each other for best amplifier performance. See the **Proper Selection of External Components** section for more information. A differential amplifier works in a manner where the difference between the two input signals is amplified. In most applications, this would require input signals that are 180° out of phase with each other. The LM4923 can be used, however, as a single ended input amplifier while still retaining its fully differential benefits. In fact, completely unrelated signals may be placed on the input pins. The LM4923 simply amplifies the difference between them.

All of these applications provide what is known as a "bridged mode" output (bridge-tied-load, BTL). This results in output signals at  $V_{\rm o1}$  and  $V_{\rm o2}$  that are 180° out of phase with respect to each other. Bridged mode operation is different from the single-ended amplifier configuration that connects the load between the amplifier output and ground. A bridged amplifier design has distinct advantages over the single-ended configuration: it provides differential drive to the load, thus doubling maximum possible output swing for a specific supply voltage. Four times the output power is possible compared with a single-ended amplifier under the same conditions. This increase in attainable output power as-

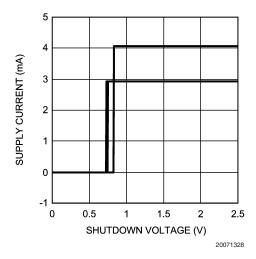

#### **Supply Current Shutdown Voltage**

sumes that the amplifier is not current limited or clipped. In order to choose an amplifier's closed-loop gain without causing excess clipping, please refer to the **Audio Power Amplifier Design** section.

A bridged configuration, such as the one used in the LM4923, also creates a second advantage over singleended amplifiers. Since the differential outputs, Vo1 and Vo2, are biased at half-supply, no net DC voltage exists across the load. This assumes that the input resistor pair and the feedback resistor pair are properly matched (see Proper Selection of External Components). BTL configuration eliminates the output coupling capacitor required in singlesupply, single-ended amplifier configurations. If an output coupling capacitor is not used in a single-ended output configuration, the half-supply bias across the load would result in both increased internal IC power dissipation as well as permanent loudspeaker damage. Further advantages of bridged mode operation specific to fully differential amplifiers like the LM4923 include increased power supply rejection ratio, common-mode noise reduction, and click and pop reduction.

## EXPOSED-DAP PACKAGE PCB MOUNTING CONSIDERATIONS

The LM4923's exposed-DAP (die attach paddle) package (LLP) provide a low thermal resistance between the die and the PCB to which the part is mounted and soldered. This allows rapid heat transfer from the die to the surrounding PCB copper traces, ground plane and, finally, surrounding air. Failing to optimize thermal design may compromise the LM4923's high power performance and activate unwanted, though necessary, thermal shutdown protection. The LLP package must have its DAP soldered to a copper pad on the PCB. The DAP's PCB copper pad is connected to a large plane of continuous unbroken copper. This plane forms a thermal mass and heat sink and radiation area. Place the heat sink area on either outside plane in the case of a two-sided PCB, or on an inner layer of a board with more than two layers. Connect the DAP copper pad to the inner layer or backside copper heat sink area with a thermal via.

### **Application Information** (Continued)

The via diameter should be 0.012in - 0.013in. Ensure efficient thermal conductivity by plating-through and solder-filling the vias.

Best thermal performance is achieved with the largest practical copper heat sink area. In all circumstances and conditions, the junction temperature must be held below 150°C to prevent activating the LM4923's thermal shutdown protection. The LM4923's power de-rating curve in the Typical Performance Characteristics shows the maximum power dissipation versus temperature. Example PCB layouts are shown in the Demonstration Board Layout section. Further detailed and specific information concerning PCB layout, fabrication, and mounting an LLP package is available from National Semiconductor's package Engineering Group under application note AN1187.

## PCB LAYOUT AND SUPPLY REGULATION CONSIDERATIONS FOR DRIVING $4\Omega$ LOADS

Power dissipated by a load is a function of the voltage swing across the load and the load's impedance. As load impedance decreases, load dissipation becomes increasingly dependent on the interconnect (PCB trace and wire) resistance between the amplifier output pins and the load's connections. Residual trace resistance causes a voltage drop, which results in power dissipated in the trace and not in the load as desired. This problem of decreased load dissipation is exacerbated as load impedance decreases. Therefore, to maintain the highest load dissipation and widest output voltage swing, PCB traces that connect the output pins to a load must be as wide as possible.

Poor power supply regulation adversely affects maximum output power. A poorly regulated supply's output voltage decreases with increasing load current. Reduced supply voltage causes decreased headroom, output signal clipping, and reduced output power. Even with tightly regulated supplies, trace resistance creates the same effects as poor supply regulation. Therefore, making the power supply traces as wide as possible helps maintain full output voltage swing.

#### POWER DISSIPATION

Power dissipation is a major concern when designing a successful amplifer, whether the amplifier is bridged or single-ended. Equation 2 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2 / (2\pi^2 R_L) \text{ Single-Ended}$$

(2)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation versus a single-ended amplifier operating at the same conditions.

$$P_{DMAX} = 4 * (V_{DD})^2 / (2\pi^2 R_L) Bridge Mode$$

(3)

Since the LM4923 has bridged outputs, the maximum internal power dissipation is 4 times that of a single-ended amplifier. Even with this substantial increase in power dissipation, the LM4923 does not require additional heatsinking

under most operating conditions and output loading. From Equation 3, assuming a 5V power supply and an  $8\Omega$  load, the maximum power dissipation point is 625mW. The maximum power dissipation point obtained from Equation 3 must not be greater than the power dissipation results from Equation 4:

$$P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

The LM4923's  $\theta_{JA}$  in an LQB08A package is 140°C/W. Depending on the ambient temperature, TA, of the system surroundings, Equation 4 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 3 is greater than that of Equation 4, then either the supply voltage must be decreased, the load impedance increased, the ambient temperature reduced, or the  $\theta_{\text{JA}}$  reduced with heatsinking. In many cases, larger traces near the output, V<sub>DD</sub>, and GND pins can be used to lower the  $\theta_{JA}$ . The larger areas of copper provide a form of heatsinking allowing higher power dissipation. For the typical application of a 5V power supply, with an  $8\Omega$  load, the maximum ambient temperature possible without violating the maximum junction temperature is approximately 62°C provided that device operation is around the maximum power dissipation point. Recall that internal power dissipation is a function of output power. If typical operation is not around the maximum power dissipation point, the LM4923 can operate at higher ambient temperatures. Refer to the Typical Performance Characteristics curves for power dissipation information.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection ratio (PSRR). The capacitor location on both the bypass and power supply pins should be as close to the device as possible. A larger half-supply bypass capacitor improves PSRR because it increases half-supply stability. Typical applications employ a 5V regulator with 10µF and 0.1µF bypass capacitors that increase supply stability. This, however, does not eliminate the need for bypassing the supply nodes of the LM4923. The LM4923 will operate without the bypass capacitor CB, although the PSRR may decrease. A 1µF capacitor is recommended for C<sub>B</sub>. This value maximizes PSRR performance. Lesser values may be used, but PSRR decreases at frequencies below 1kHz. The issue of C<sub>B</sub> selection is thus dependant upon desired PSRR and click and pop performance as explained in the section **Proper Selection of External Components.**

#### SHUTDOWN FUNCTION

In order to reduce power consumption while not in use, the LM4923 contains shutdown circuitry that is used to turn off the amplifier's bias circuitry. The device may then be placed into shutdown mode by toggling the Shutdown Select pin to logic low. The trigger point for shutdown is shown as a typical value in the Supply Current vs Shutdown Voltage graphs in the **Typical Performance Characteristics** section. It is best to switch between ground and supply for maximum performance. While the device may be disabled with shutdown voltages in between ground and supply, the idle current may be greater than the typical value of 0.1µA. In either case, the shutdown pin should be tied to a definite voltage to avoid unwanted state changes.

In many applications, a microcontroller or microprocessor output is used to control the shutdown circuitry, which pro-

### **Application Information** (Continued)

vides a quick, smooth transition to shutdown. Another solution is to use a single-throw switch in conjunction with an external pull-up resistor. This scheme guarantees that the shutdown pin will not float, thus preventing unwanted state changes.

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components in applications using integrated power amplifiers is critical when optimizing device and system performance. Although the LM4923 is tolerant to a variety of external component combinations, consideration of component values must be made when maximizing overall system quality.

The LM4923 is unity-gain stable, giving the designer maximum system flexibility. The LM4923 should be used in low closed-loop gain configurations to minimize THD+N values and maximize signal to noise ratio. Low gain configurations require large input signals to obtain a given output power. Input signals equal to or greater than 1Vrms are available from sources such as audio codecs. Please refer to the Audio Power Amplifier Design section for a more complete explanation of proper gain selection. When used in its typical application as a fully differential power amplifier the LM4923 does not require input coupling capacitors for input sources with DC common-mode voltages of less than  $V_{\rm DD}$ . Exact allowable input common-mode voltage levels are actually a function of  $V_{\rm DD}$ ,  $R_{\rm i}$ , and  $R_{\rm f}$  and may be determined by Equation 5:

$$V_{CMi} \le (V_{DD}-1.2)^*((R_f+(R_i)/(R_f)-V_{DD}^*(R_i/2R_f))$$

(5)

$$-R_F / R_I = A_{VD}$$

(6)

Special care must be taken to match the values of the feedback resistors ( $R_{\text{F1}}$  and  $R_{\text{F2}})$  to each other as well as matching the input resistors ( $R_{\text{i1}}$  and  $R_{\text{i2}})$  to each other (see Figure 1) more in front. Because of the balanced nature of differential amplifiers, resistor matching differences can result in net DC currents across the load. This DC current can increase power consumption, internal IC power dissipation, reduce PSRR, and possibly damaging the loudspeaker. The chart below demonstrates this problem by showing the effects of differing values between the feedback resistors while assuming that the input resistors are perfectly matched. The results below apply to the application circuit shown in Figure 1, and assumes that  $V_{\text{DD}} = 5V,\,R_{\text{L}} = 8\Omega,$  and the system has DC coupled inputs tied to ground.

| Tolerance | R <sub>F1</sub> | R <sub>F2</sub> | V <sub>02</sub> - V <sub>01</sub> | I <sub>LOAD</sub> |

|-----------|-----------------|-----------------|-----------------------------------|-------------------|

| 20%       | 0.8R            | 1.2R            | -0.500V                           | 62.5mA            |

| 10%       | 0.9R            | 1.1R            | -0.250V                           | 31.25mA           |

| 5%        | 0.95R           | 1.05R           | -0.125V                           | 15.63mA           |

| 1%        | 0.99R           | 1.01R           | -0.025V                           | 3.125mA           |

| 0%        | R               | R               | 0                                 | 0                 |

Similar results would occur if the input resistors were not carefully matched. Adding input coupling capacitors in between the signal source and the input resistors will eliminate this problem, however, to achieve best performance with

minimum component count it is highly recommended that both the feedback and input resistors matched to 1% tolerance or better.

#### **AUDIO POWER AMPLIFIER DESIGN**

#### Design a 1W/8 $\Omega$ Audio Amplifier

Given:

Power Output1WrmsLoad Impedance $8\Omega$ Input Level1VrmsInput Impedance $20k\Omega$ Bandwidth $100Hz-20kHz \pm 0.25dB$

A designer must first determine the minimum supply rail to obtain the specified output power. The supply rail can easily be found by extrapolating from the Output Power vs Supply Voltage graphs in the **Typical Performance Characteristics** section. A second way to determine the minimum supply rail is to calculate the required  $V_{\rm OPEAK}$  using Equation 7 and add the dropout voltages. Using this method, the minimum supply voltage is (Vopeak + ( $V_{\rm DO\ TOP}$  + ( $V_{\rm DO\ BOT}$ )), where  $V_{\rm DO\ BOT}$  and  $V_{\rm DO\ TOP}$  are extrapolated from the Dropout Voltage vs Supply Voltage curve in the **Typical Performance Characteristics** section.

$$V_{\text{opeak}} = \sqrt{(2R_{L}P_{0})}$$

(7)

Using the Output Power vs Supply Voltage graph for an  $8\Omega$  load, the minimum supply rail just about 5V. Extra supply voltage creates headroom that allows the LM4923 to reproduce peaks in excess of 1W without producing audible distortion. At this time, the designer must make sure that the power supply choice along with the output impedance does not violate the conditions explained in the **Power Dissipation** section. Once the power dissipation equations have been addressed, the required differential gain can be determined from Equation 8.

$$A_{VD} \ge \sqrt{(P_0 R_L)}/(V_{IN}) = V_{orms}/V_{inrms}$$

(8)

$$R_f / R_i = A_{VD}$$

From Equation 7, the minimum  $A_{VD}$  is 2.83. Since the desired input impedance was  $20k\Omega,$  a ratio of 2.83:1 of  $R_f$  to  $R_i$  results in an allocation of  $R_i=20k\Omega$  for both input resistors and  $R_f=60k\Omega$  for both feedback resistors. The final design step is to address the bandwidth requirement which must be stated as a single -3dB frequency point. Five times away from a -3dB point is 0.17dB down from passband response which is better than the required  $\pm 0.25dB$  specified.

$$f_H = 20kHz * 5 = 100kHz$$

The high frequency pole is determined by the product of the desired frequency pole,  $f_{\rm H}$ , and the differential gain,  $A_{\rm VD}$ . With a  $A_{\rm VD}=2.83$  and  $f_{\rm H}=100 {\rm kHz}$ , the resulting GBWP = 150 kHz which is much smaller than the LM4923 GBWP of 10 MHz. This figure displays that if a designer has a need to design an amplifier with a higher differential gain, the LM4923 can still be used without running into bandwidth limitations.

### Physical Dimensions inches (millimeters) unless otherwise noted (8X 0.3) (□0.8) (1.2 TYP) (8X 45°X0.1) DIMENSIONS ARE IN MILLIMETERS RECOMMENDED LAND PATTERN 1:1 RATIO WITH PKG SOLDER PADS - 8X 0.4±0.05 - 0.1 C A B (0.1 TYP) PIN 1 INDEX AREA 8X 0.3±0.1 □0.8±0.1 2 + 0 . 1 4X 0.25) В

# NS Package Number LQB08A

LQ Package Order Number LM4923LQ

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2 ± 0 . 1

A

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

4X 0.65

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

**National Semiconductor** Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

LQB08A (Rev A)